Direct Memory Access

Direct Memory Access (DMA) is a data transfer technique used in computer systems to move data directly between memory and peripheral devices without continuous CPU involvement.

In a traditional system, the CPU manages all data transfers between the peripheral devices and memory. It will slow down overall performance when large amounts of data need to be moved. A specialized controller is used in the system that overcomes this limitation by taking control of the system bus during data transfer, allowing the CPU to perform other operations simultaneously.

This mechanism significantly improves data transfer speed, system efficiency, and multitasking capability, making it essential in applications that involve high-speed data movement, such as disk operations, audio/video processing, and communication systems. By reducing CPU overhead and enabling parallel processing, DMA plays a crucial role in modern embedded systems, microcontrollers, and computer architectures.

Data transfer in a Direct Memory Access system is managed by a specialized hardware component known as the DMA Controller (DMAC). This controller enables efficient data transfer between memory and peripheral devices with minimal processor involvement.

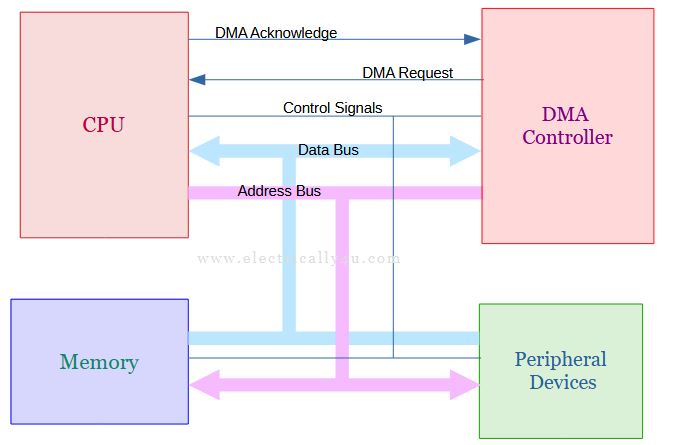

During a DMA operation, the system’s address and data buses are temporarily allocated to the I/O device connected through the DMAC, making them unavailable to the CPU. In computer systems, for instance, data transfer between the hard disk and main memory typically takes place through DMA channels.

Working of Direct Memory Access

A typical DMA process begins when a specific event, such as the arrival of new data, alerts the DMA controller that a transfer is required. The DMAC then sends a DMA request (DRQ) signal to the CPU, asking for permission to access the system bus.

Once the CPU finishes its current operation, it releases control of the bus and sends back a DMA acknowledge (DACK) signal, allowing the DMAC to proceed.

The DMA controller then performs the data transfer by reading from or writing to memory, controlling the address, data, and control lines as if it were the CPU itself.

When the transfer is completed, the DMAC stops driving the bus, withdraws the DMA request, and returns control of the bus to the CPU, which then resumes its normal operations.

In each DMA cycle, the controller carries out either a read operation from a peripheral followed by a write to memory, or a read from memory followed by a write to a peripheral. The DMA controller does not process or modify the data; it simply transfers the bytes according to the instructions specified in its configuration registers.

DMA controllers must be initialized through software before they can perform data transfers. The initialization process typically involves configuring parameters such as the source and destination base addresses, the size of the data block, and the settings for processor interrupts to occur before or after the transfer.

In many systems, the DMA controller can be set to automatically increment one or both addresses after each byte or word transfer, ensuring that subsequent data is moved to or from the next memory location. However, in transfers between memory and certain peripherals, the peripheral address often remains fixed, meaning that each byte of data is transferred to or from the same address, depending on the device’s requirements.

Modes of Operation

There are four modes of operation in direct memory access. They are explained as follows.

Burst Mode: In burst mode, the DMA controller transfers an entire block of data in one continuous sequence. Once the CPU grants access to the DMA controller to use the system buses, the controller transmits all the data bytes before returning control of the buses to the CPU. This mode is useful for tasks such as loading large programs or data files into memory. However, during this process, the CPU remains inactive for a relatively long duration, as it cannot access the buses until the transfer is complete.

Cycle Stealing mode: In cycle stealing mode, the DMA controller transfers one byte (or word) of data at a time and then releases the bus back to the CPU. It “steals” a single clock cycle from the CPU during each transfer. It is used when continuous CPU operation is important, such as in real-time systems.

Transparent Mode: In this mode, the DMA controller transfers data only when the CPU is not using the system bus (during idle cycles). This makes the DMA operation invisible or “transparent” to the CPU. It is suitable for background data transfers that are not time-critical.

Demand mode: In this, the data transfer continues as long as the peripheral device requests it. When the device’s request signal is deactivated, the transfer pauses and resumes when the request is reactivated. It is commonly used in devices like printers and data acquisition systems.

Advantages of Direct Memory Access

- The data transfer speed is fast due to the non-intervention of the CPU.

- Offloading data transfer to DMA increases the overall speed and responsiveness of the system, especially in multitasking.

- Improve the system efficiency.

- The program complexity and instruction count will be reduced.

- Because the CPU can stay in a low-power state during DMA operations, overall energy efficiency improves.

- DMA ensures continuous and uninterrupted data transfer, which is crucial in applications like video streaming, audio playback, and communication systems.

Disadvantages of Direct Memory Access

- It increases the hardware cost and design complexity of the system.

- Bus conflicts can occur when both CPU and DMA try to access memory simultaneously.

- Memory access control becomes more complicated, as both CPU and DMA need synchronized access to avoid data corruption.

- Although DMA reduces CPU involvement, interrupts are still needed to notify completion of transfers, which can slightly reduce efficiency.

- DMA controllers often have a limited number of channels, restricting how many devices can use DMA at once.

- DMA operations occur in the background, making it harder to trace and debug data transfer issues.

- For small amounts of data, the setup time of DMA can exceed the benefit gained, making it less efficient than direct CPU-controlled transfer.