SR Flip flop – Circuit, truth table and operation

SR flip flop, also known as SR latch is the basic and simplest type of flip flop. It is a single bit storage element. It has only two logic gates. The output of each gate is connected to the input of another gate.

The state of the SR flip flop is determined by the condition of the output Q. If its value is 1, then the state is said to be SET and if Q = 0, the state is said to be RESET. Hence it is called SR flip flop.

The SR flipflop can be constructed by using NAND gates or NOR gates. In the following section, let us learn at SR flip flop in detail.

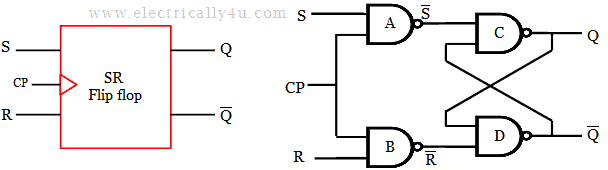

SR flip flop

It has two active-low inputs S’, R’ and two outputs Q, Q’.

Operation and truth table

When S’ = 0, R’ = 0, the respective next state outputs will be Q+1 = 1 and Q’+1 = 1, which is not allowed, since both are complement to each other.

When the inputs are S’ = 0, R’ = 1, irrespective of the value of Q’, the next state output of NAND gate A is logic HIGH, i.e Q+1 = 1, which will SET the flip flop. So the two inputs of NAND gate B are R’ = 1 and Q = 1. The output thus produced is Q’+1 = 0.

For the inputs S’ = 1, R’ = 0, irrespective of the values of Q, the next state output of NAND gate B is logic HIGH, i.e, Q’+1 = 1. The two inputs for NAND gate A are S’ = 1 and Q’ = 1, producing an output Q+1 = 0, which will RESET the flip flop.

When the inputs are S’ = 1, R’ = 1 and the present state outputs are Q = 1 and Q’ = 0, then the next state output produced from the NAND gate A is Q+1 = 1. If Q = 0 and Q’ = 1, the next state output is Q+1 = 0. In this case, there is no change in the output state.

Clocked SR Flip flop

The Clocked SR flip-flop consists of 4 NAND gates, two inputs(S and R) and two outputs(Q and Q’). The clock pulse is given at the inputs of gate A and B.

If the clock pulse input is replaced by an enable input, then it is said to be SR latch. Let us assume that this flip flop works under positive edge triggering. The following figure shows the block diagram and the logic circuit of a clocked SR flip flop.

No Change state[S = 0, R = 0]

When the clock pulse is applied, the output of NAND gates A and B will be S’ = 1, R’ = 1.

For this case, if Q = 0, Q’ = 1, then both the inputs for NAND gate C are 1 and the output thus produced by gate C is Q+1 =0. The present state output is Q = 0 and the next state output is Q’ = 0. Thus the state has no change.

For the same SR inputs, if Q = 1, Q’ = 0, the inputs for NAND gate C will be 0 and 1. For these inputs, the output produced by the NAND gate is Q+1 = 1, hence there is no change in the state.

RESET state[S = 0, R = 1]

Upon the application of the clock pulse, the output of NAND gate A and B are S’ = 1, R’ = 0.

Let the present state output be Q = 0 or Q = 1. For any of these inputs at the NAND gate D, the next state output produced is Q’+1 = 1. Now, the tw0 inputs for NAND gate C are S’ = 1, Q’ = 1, which produces an output at next state as Q+1 = 0.

For this case, whether the present state is either 0 or 1, it will produce an output 0, which will RESET the flip flop.

SET state[S = 1, R = 0]

When the clock pulse is applied, the output from the NAND gate A and B are S’ = 0, R’ = 1.

For this condition, irrespective of the present state input Q’, the next state output produced by the NAND gate C is Q+1 = 1. Thus the two inputs of NAND gate D are R’ = 1 and Q = 1, which produces an output Q’+1 = 0.

So, in this case, whether the present state output is either 0 or 1, the next state output is logic 1, which will SET the flip flop.

Indeterminate or Invalid state[S = 1, R = 1]

For the inputs S = 1 and R = 1, the NAND gates A and B produces the output S’ = 0, R’ = 0.

Now, if Q = 0 and Q’ = 1, the inputs for NAND gate C will be S’ = 0 and Q’ = 1. The output produced from NAND gate C is Q+1 = 1. Similarly, the two inputs for NAND gate D will be R’ = 0 and Q = 0. The output produced from the NAND gate D is Q’+1 = 1.

If Q = 1 and Q’ = 0, the output produced from the NAND gate C is Q+1 = 1 for the inputs S’ = 0 and Q’ = 0. For the same value of Q and Q’, output produced from NAND gate D is Q’+1 = 1, where the inputs are R’ = 0 and Q = 1.

For this case, it is observed that the next state output Q+1 = 1 and Q’+1 = 1. This is an impossible output because Q and Q’ should be complement with each other. So it is an indeterminate or invalid state.

Switching diagram of clocked SR Flip flop

The following figure shows the switching diagram of clocked SR flip flop.